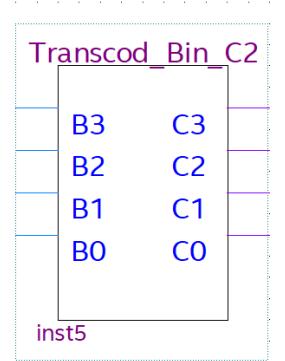

## Transcodeur Binaire/Complément à 2

Un transcodeur « Binaire-Complément à 2 » convertit un nombre binaire d'entrée (B3 B2 B1 B0) en son complément à 2, qui est aussi codé sur 4 bits (C3 C2 C1 C0). Le complément à 2 d'un nombre se calcule en inversant tous les bits (complément à 1) et en ajoutant 1 au résultat.

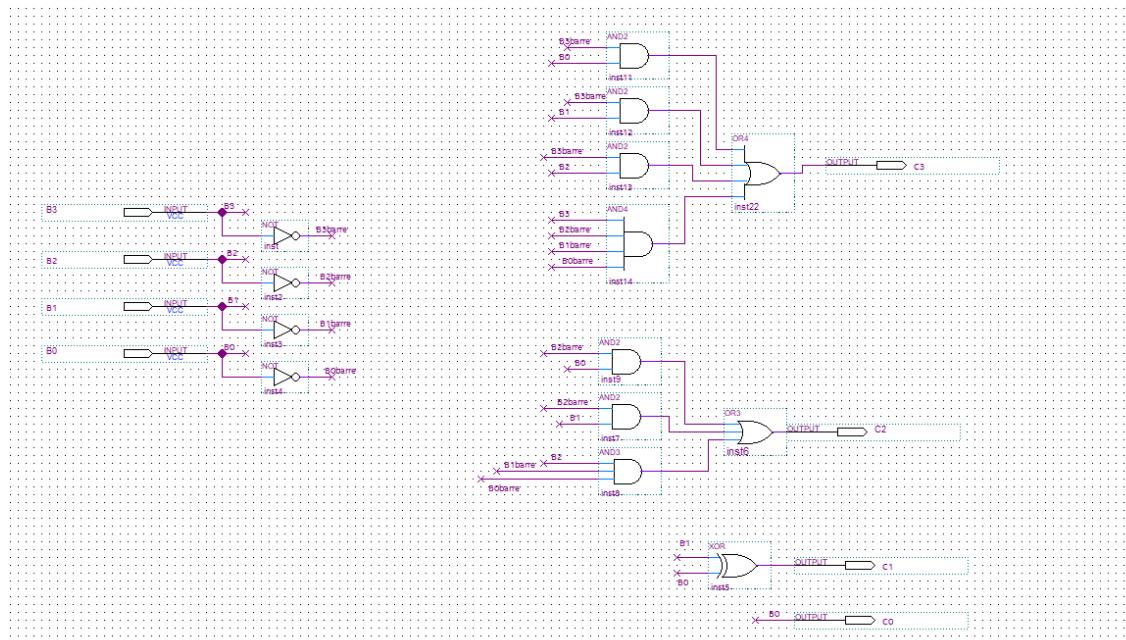

### Équations logiques des sorties en fonction des entrées :

$$C0 = B0$$

$$C3 = (\sim B3 \& B0) | (\sim B3 \& B1) | (\sim B3 \& B2) | (B3 \& \sim B2 \& \sim B1 \& \sim B0)$$

$$C1 = B1 \oplus B0$$

$$C2 = (\sim B2 \& B0) | (\sim B2 \& B1) | (B2 \& \sim B1 \& \sim B0)$$

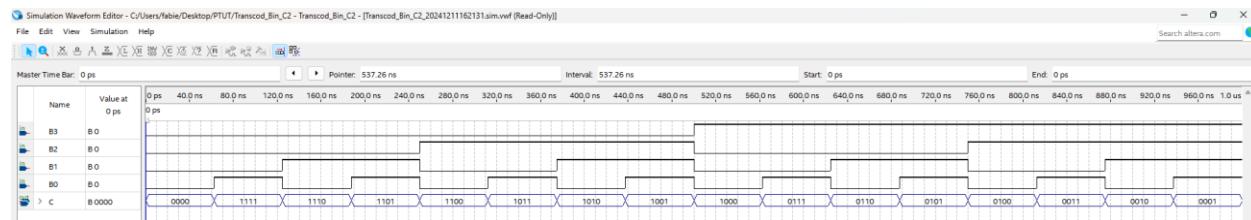

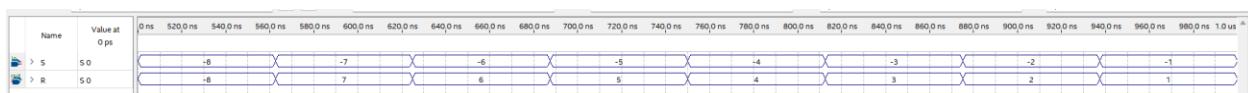

### Simulation du transcodeur :

### Schéma fonctionnel :

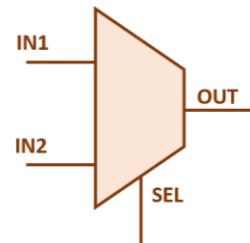

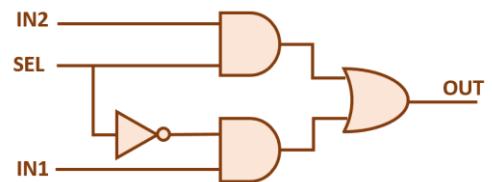

## Multiplexeur 2 x 1

Un Multiplexeur 2x1 est un circuit logique combinatoire qui sélectionne l'une des deux entrées de données (IN2 et IN1) et la transmet vers une seule sortie (OUT), en fonction de l'état d'un signal de sélection (SEL).

**Equations logiques de la sortie en fonction des entrées :**

$$\text{OUT} = \sim\text{SEL} \cdot \text{IN1} + \text{SEL} \cdot \text{IN2}$$

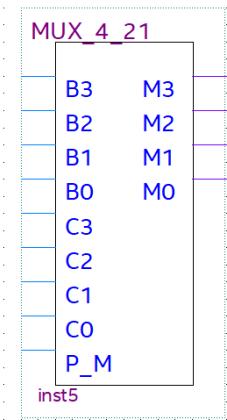

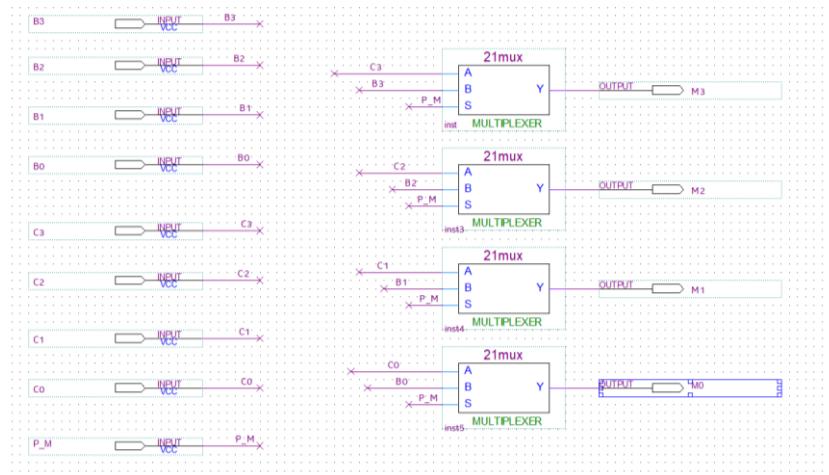

## Multiplexeur parallèle 4 x (2 x 1)

Un MUX  $4 \times (2 \times 1)$  est un circuit qui combine quatre multiplexeurs  $2 \times 1$  pour sélectionner un nombre de 4 bits parmi deux (B ou C) et l'affiche en sortie(M), en fonction d'un signal de sélection (P\_M). Chaque multiplexeur  $2 \times 1$  gère un bit distinct des deux nombres.

### Schéma fonctionnel :

### Simulation du Multiplexeur :

On observe une recopie en sortie du nombre B lorsque P\_M est à l'état **bas**, et la recopie de C avec P\_M à l'état **haut**.

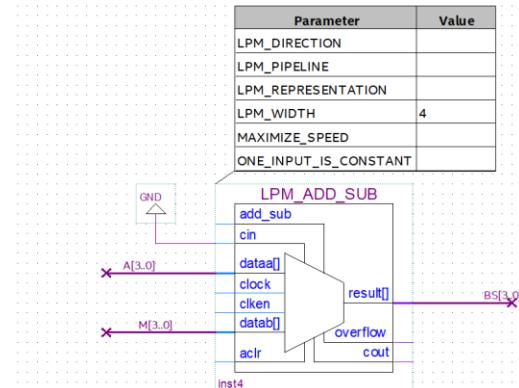

## Additionneur/Soustracteur 4 bits :

Un additionneur/ soustracteur 4 bits permet une fois couplé aux éléments détaillés dans les fiches précédentes de sommer 2 nombres codés sur 4 bits signés ainsi que de les soustraire. L'additionneur 4 bits 283 que nous utilisons permet seulement d'effectuer une somme. Pour la soustraction, une fois associé au MUX\_4\_21 (décris page 3) cela revient à sommer un nombre négatif ce qui revient à le soustraire.

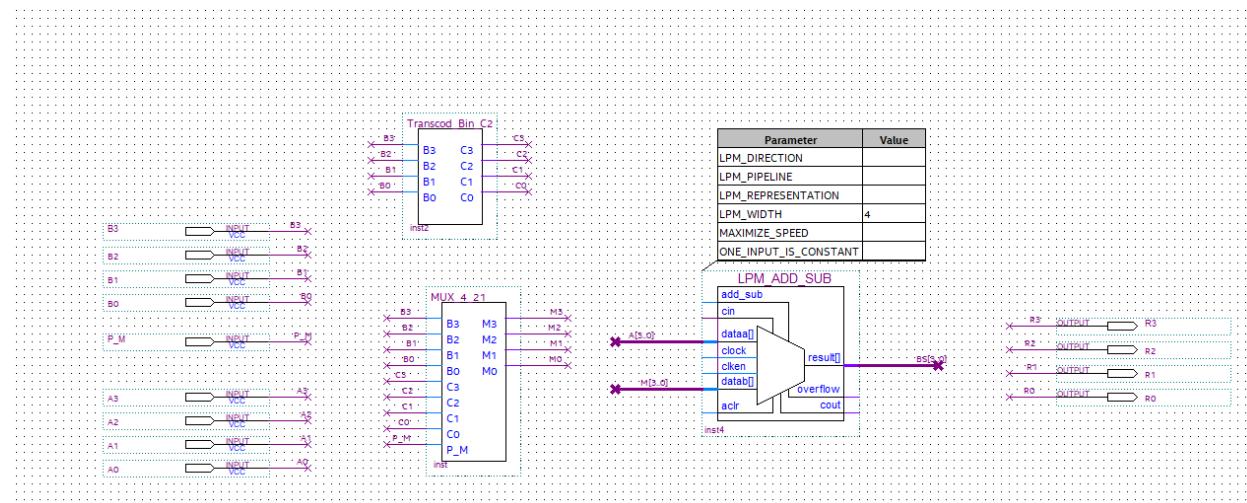

### Schéma fonctionnel de son implantation :

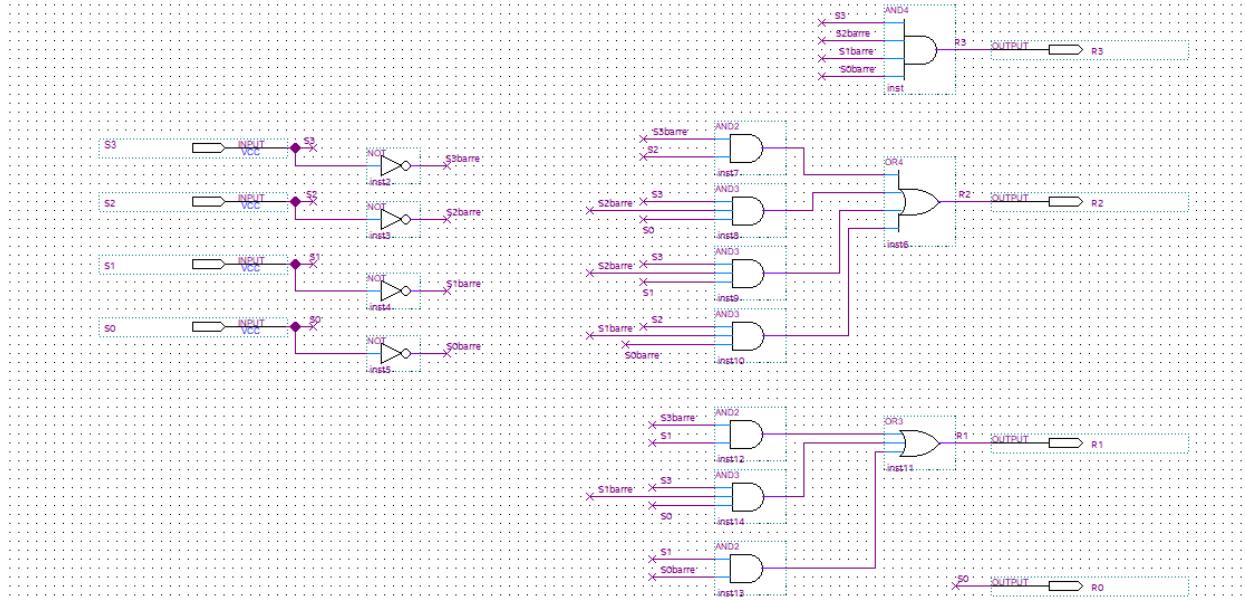

### Simulation de l'additionneur :

Quand  $P_M = 0$ , on a bien  $R = A + B$  et quand  $P_M = 1$ ,  $R = A - B$ .

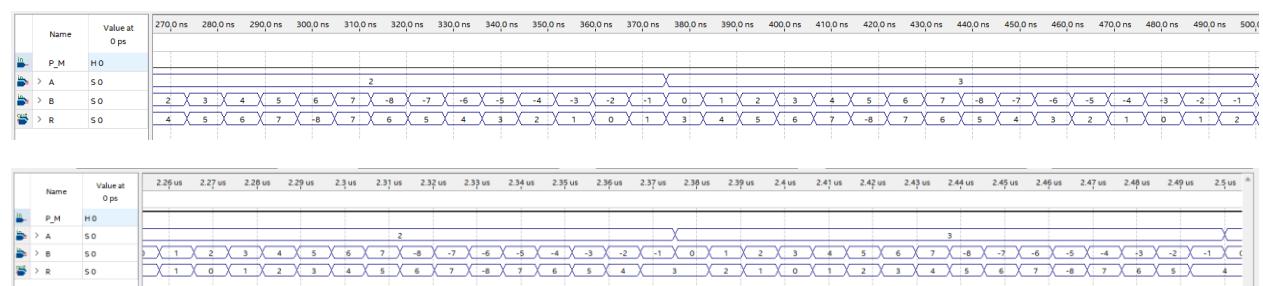

## Transcodeur Binaire signé / Binaire :

Un transcodeur « Binaire signé-Binaire » convertit un nombre binaire signé d'entrée (S3 S2 S1 S0) en son équivalent en binaire non signé, codé sur 4 bits (R3 R2 R1 R0). Pour un nombre signé négatif (S3 = 1), la conversion s'effectue en prenant le complément à 2 du nombre d'entrée, tandis que pour un nombre signé positif (S3 = 0), la valeur reste inchangée.

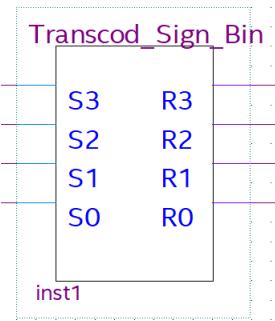

### Equations logiques des sorties en fonction des entrées :

$$R3 = (S3 \& \sim S2 \& \sim S1 \& \sim S0)$$

$$R2 = (\sim S3 \& S2) \mid (S3 \& \sim S2 \& S0) \mid (S3 \& \sim S2 \& S1) \mid (S2 \& \sim S1 \& \sim S0)$$

$$R1 = (\sim S3 \& S1) \mid (S3 \& \sim S1 \& S0) \mid (S1 \& \sim S0)$$

$$R0 = S0$$

### Schéma fonctionnel :

### Simulation du transcodeur :

On observer que la sortie recopie l'entrée en retirant le signe, convertissant alors une

nombre binaire signé en binaire non signé.